丂僸僔僥儕僗僐儞僷儗乕僞夞楬偺専摙傪偟傑偡丅

乮侾乯昡壙夞楬

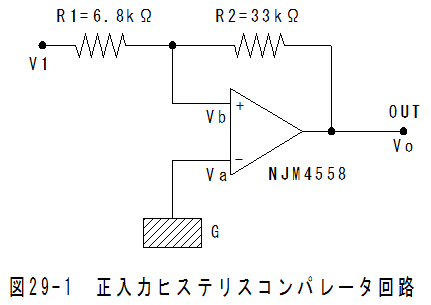

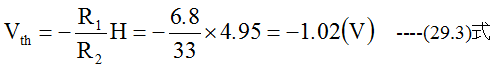

丂惓擖椡僸僔僥儕僗僐儞僷儗乕僞夞楬傪恾29-1偵帵偟傑偡丅

丂

乮俀乯惓擖椡僸僔僥儕僗僐儞僷儗乕僞夞楬楬偺弌椡揹埑

丂恾29-1偵偍偄偰

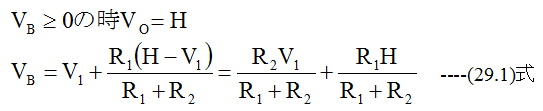

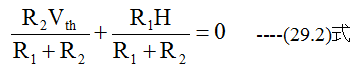

Vb=0偲側傞揹埑傪Vth偲偡傞側傜偽

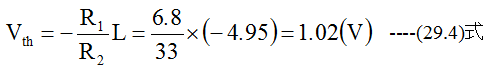

(29.2)幃傪曄宍偡傞偲

Vb亝0偺帪丄Vo亖L偲側傝傑偡丅偙偺応崌傕摨條偵

偲側傝傑偡丅

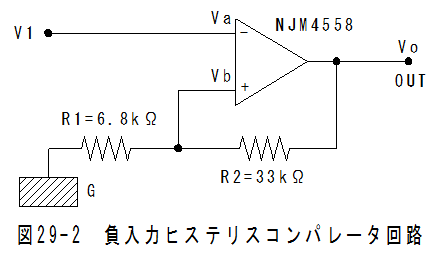

乮侾乯昡壙夞楬

丂晧擖椡僸僔僥儕僗僐儞僷儗乕僞夞楬傪恾29-2偵帵偟傑偡丅

丂

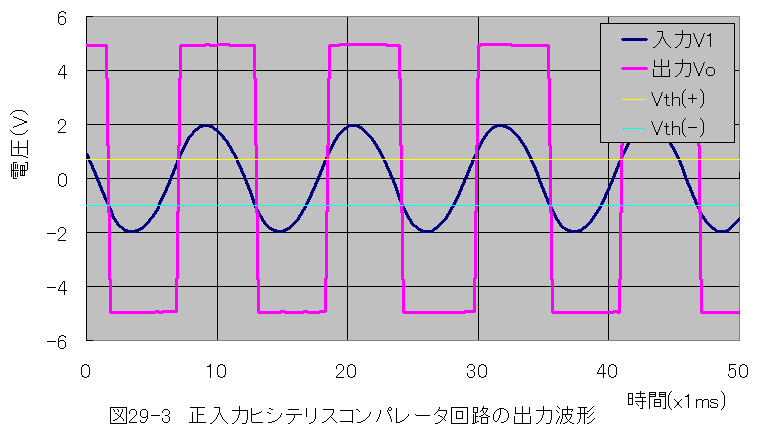

乮俀乯晧擖椡僸僔僥儕僗僐儞僷儗乕僞夞楬偺弌椡揹埑

丂恾29-2偵偍偄偰偼

偲側傝傑偡丅

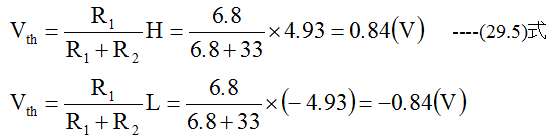

丂惓尫攇傪擖椡帪偺惓擖椡僸僔僥儕僗僐儞僷儗乕僞夞楬傪娙堈僆僔儘偱娤嶡偟偨寢壥傪恾29-3偵帵偟傑偡丅

恾29-3偵偍偄偰埲壓偺傛偆偵側傝傑偟偨丅

乮侾乯擖椡V1乮惓尫攇乯揹埑亖1.98V

乮俀乯弌椡Vo乮曽宍攇乯揹埑亖4.95V

乮俁乯乯僾儔僗懁鑷抣亖0.699V乮寁嶼抣亖1.02倴乯

乮係乯儅僀僫僗懁鑷抣亖-0.99V乮寁嶼抣亖-1.02倴乯

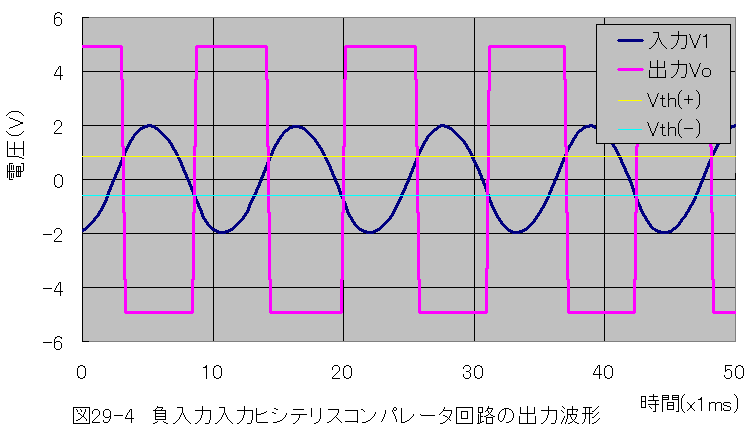

丂惓尫攇傪擖椡帪偺晧擖椡僸僔僥儕僗僐儞僷儗乕僞夞楬傪娙堈僆僔儘偱娤嶡偟偨寢壥傪恾29-4偵帵偟傑偡丅

恾29-4偵偍偄偰埲壓偺傛偆偵側傝傑偟偨丅

乮侾乯擖椡V1乮惓尫攇乯揹埑亖1.98V

乮俀乯弌椡Vo乮曽宍攇乯揹埑亖4.93V

乮俁乯乯僾儔僗懁鑷抣亖0.845V乮寁嶼抣亖0.84倴乯

乮係乯儅僀僫僗懁鑷抣亖-0.593V乮寁嶼抣亖-0.84倴乯

乮侾乯僸僔僥儕僗僐儞僷儗乕僞夞楬偼鑷抣偑僾儔僗懁偲儅僀僫僗懁偵敪惗偟偰僸僗僥儕僗偑惗偠傑偡丅

乮俀乯僸僗僥儕僗偼僠儍僞儕儞僌傪杊巭偡傞忋偱桳岠偵嶌梡偟傑偡丅

乮俁乯惓擖椡僸僔僥儕僗僐儞僷儗乕僞夞楬偱偼丄僾儔僗懁鑷抣偑寁嶼抣偲幚應抣偺岆嵎偑戝偒偄丅

乮係乯晧擖椡僸僔僥儕僗僐儞僷儗乕僞夞楬偱偼丄儅僀僫僗懁鑷抣偑寁嶼抣偲幚應抣偺岆嵎偑戝偒偄丅

乮俆乯娙堈僆僔儘偺應掕壜擻揹埑偼0乣5V偱儅僀僫僗懁傪應掕偱偒傑偣傫丅娙堈僆僔儘偺擖椡偼掞峈暘埑偱揹埑傪挷惍偟傑偟偨丅

乮俇乯娙堈僆僔儘偼弌椡攇宍偺僌儔儞僪婎弨偱應掕偱偒傑偣傫丅僆僼僙僢僩傪梌偊偰應掕偡傞偨傔丄僆僼僙僢僩岆嵎偑敪惗偟傑偡丅

乮俈乯僆僼僙僢僩岆嵎偼應掕屻曗惓偟傑偟偨丅